象芯3號物聯網晶片的規格書

2026-03-02

TP6300-數據手冊-V1.0 (象芯3號晶片的規格書)

TP6300 晶片採用 S-FSK 技術

目 錄

TP6300數據手冊

1 概述

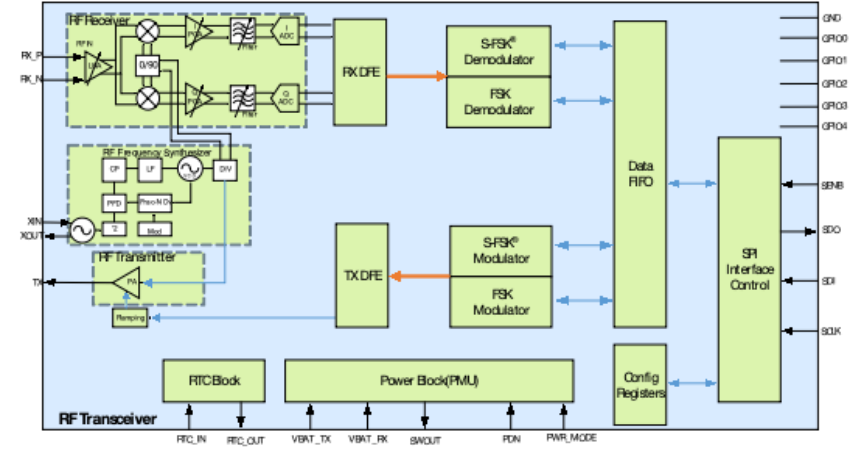

1.1 簡化方框圖

數據機

可完成S-FSK SIMS信號的調製及解調;

射頻模組

頻率支持SUB-1G頻率

主要介面

- 1組 SPI;

- 5個GPIO;

- Xtal_clk輸出,晶體輸出,給外部其餘晶片作為參考時鐘使用;

- 支持外部32.786KHz時鐘

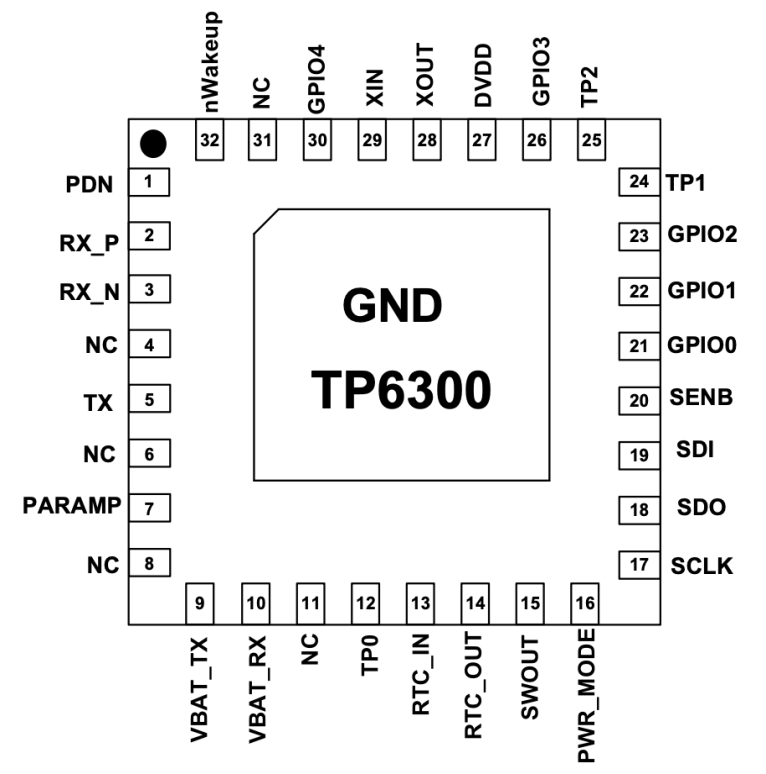

1.2 引腳及描述

- 圖 1.1 TP6300 引腳圖

表 1-1 TP6300引腳描述表

| 引腳號 | 引腳名稱 | I/O | 描述 |

| 1 | PDN | I | 外部power down,低電平有效,高電平為工作狀態 |

| 2 | RX_P | I | 射頻接收端口,差分輸入 |

| 3 | RX_N | ||

| 4 | NC | 正常使用NC懸空 | |

| 5 | TX | O | PA輸出 |

| 6 | NC | 正常使用NC懸空 | |

| 7 | PA_RAMP | O | PA RAMP電壓輸出,控制外部PA |

| 8 | NC | 正常使用NC懸空 | |

| 9 | VBAT _TX | Power | TX鏈路電源 |

| 10 | VBAT _RX | Power | RX鏈路電源 |

| 11 | NC | 正常使用NC懸空 | |

| 12 | TP0 | 晶片測試用途,正常使用NC懸空 | |

| 13 | RTC_IN | I | 外部32K晶體輸入端,低功耗模式時使用 |

| 14 | RTC_OUT | O | 外部32K晶體輸出端,低功耗模式時使用 |

| 15 | SWOUT | O | DCDC 輸出端 |

| 16 | PWR_MODE | I | PMU模式選擇:NC =LDO模式,VBAT _RX接VBAT接低=DCDC模式,VBAT_RX接SWOUT |

| 17 | SCLK | I | SPI時鐘信號 |

| 18 | SDO | O | SPI數據輸出 |

| 19 | SDI | I | SPI數據輸入 |

| 20 | SENB | I | SPI線選信號 |

| 21 | GPIO0 | I/O | 通用GPIO介面,GPIO複用關係見下麵章節 |

| 22 | GPIO1 | I/O | 通用GPIO介面,GPIO複用關係見下麵章節 |

| 23 | GPIO2 | I/O | 通用GPIO介面,GPIO複用關係見下麵章節 |

| 24 | TP1 | 晶片測試用途,正常使用NC懸空 | |

| 25 | TP2 | 晶片測試用途,正常使用NC懸空 | |

| 26 | GPIO3 | I/O | 通用GPIO介面,GPIO複用關係見下麵章節 |

| 27 | DVDD | Power | 內部數字電源,推薦1uF去耦電容對地 |

| 28 | XOUT | O | 參考時鐘輸出 |

| 29 | XIN | I | 參考時鐘輸入 |

| 30 | GPIO4 | I/O | 通用GPIO介面,GPIO複用關係見下麵章節 |

| 31 | NC | 正常使用NC懸空 | |

| 32 | nWakeup | I | 用於外部喚醒功能(電平喚醒) |

| 33 | GND | 電源參考地 |

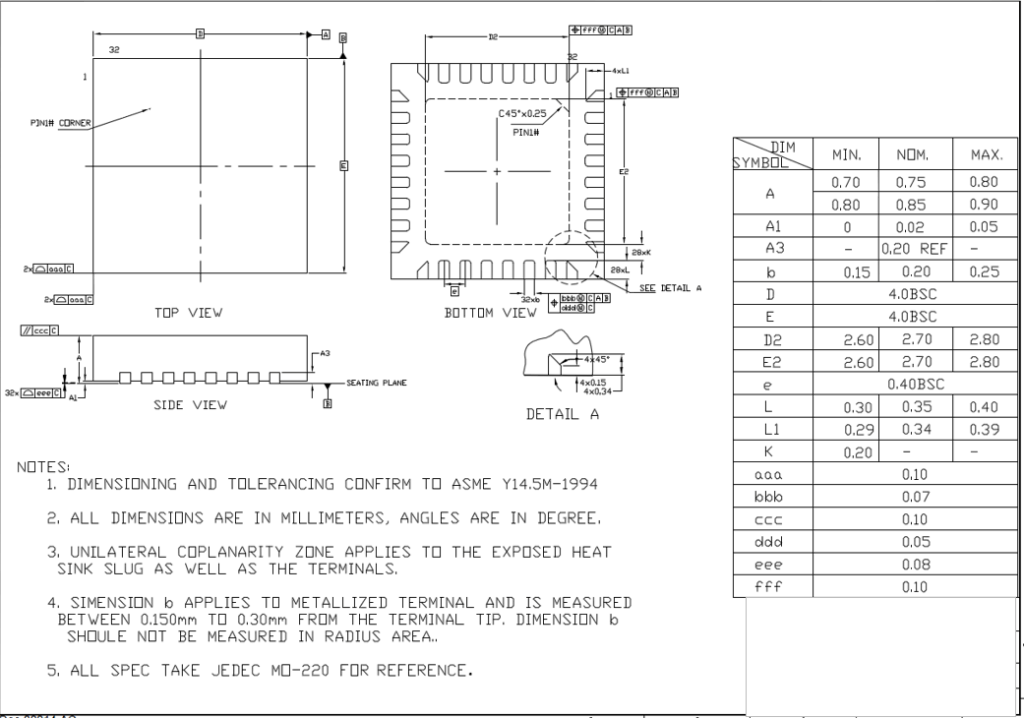

1.3 封裝尺寸

2 電氣特性

測試條件:VDD= 3.3 V,TOP= 25 °C,FRF = 470 MHz;靈敏度是通過接收一個PN9 序列及匹配至50 Ω阻抗下,5%PER 的標準下測得; 除非另行聲明,所有結果都是在EVB評估板上測試得到。

2.1 推薦運行條件

| 符號 | 參數描述 | 最小 | 典型 | 最大 | 單位 |

| VDD | 運行電源電壓 | 1.8 | +3.6 | V | |

| TA | 運行環境溫度 | -40 | +85 | °C |

2.2 絕對最大額定值

| 符號 | 參數描述 | 最小 | 最大 | 單位 |

| VDD | 電源電壓 | -0.3 | 3.6 | V |

| Toper | 存儲溫度 | -50 | 125 | °C |

| Tj | 結溫 | -40 | 125 | °C |

| ESD level | 人體模型(HBM) | -2 | 2 | KV |

2.3 可靠性參數

| 符號 | 參數 | 條件 | 典型值 | 單位 |

| VESD(HBM) | 靜態放電電壓(人體模型) | ESDA/JEDEC JS-001-2017 | 2 | KV |

| VESD(CDM) | 靜態放電電壓(充電設備模型) | ESDA/JEDEC JS-002-2018 | 250 | V |

| LU | 靜態 Latch-Up | JESD78E | 200 | mA |

2.4 晶片規格

2.4.1 功耗規格

表 21 功耗規格*

| 參數 | 符號 | 描述 | 最小 | 典型 | 最大 | 單位 |

| 關機電流 | IShutdown | PDN=0, 所有電路均關閉 | 700 | nA | ||

| 睡眠電流* | IDeepsleep | 深睡眠模式,內部32k關閉,寄存器不保持需外部喚醒 | 1.2 | uA | ||

| ISleep | 淺睡眠模式,內部32K工作,RTC寄存器保持,其餘寄存器不保持, 可定時喚醒 | 1.4 | uA | |||

| 待機電流* | IRC | 晶片內部RC振盪器工作,晶體不工作,寄存器保持 | 1 | mA | ||

| Iosc | 晶體工作,寄存器保持 | 1.7 | mA | |||

| 頻率保持* | IPLL_ON | PLL頻率保持狀態,收發均關閉 | 10.5 | mA | ||

| 發射電流TX | ITX | 功率=0dBm | 55 | mA | ||

| 功率=5dBm | 60 | mA | ||||

| 功率=10dBm | 75 | mA | ||||

| 功率=17dBm | 106 | mA | ||||

| 功率=20dBm | 130 | mA | ||||

| 功率=22dBm | 160 | mA | ||||

| 接收電流 | IRX | RX模式 | 55 | mA |

2.4.2 頻率綜合器

表 22 頻率綜合器規格

| 參數 | 符號 | 描述 | 最小 | 典型 | 最大 | 單位 |

| 頻率範圍 | FSYN | 40 | 530 | MHz | ||

| 710 | 1050 | |||||

| 頻率解析度 | FRES | 20 | Hz | |||

| 調諧時間 | TLOCK | 58 | Us | |||

| 相位雜訊230MHz | PN | 10 kHz 頻率偏移 | -106 | dBc/Hz | ||

| 100kHz 頻率偏移 | -110 | dBc/Hz | ||||

| 1MHz 頻率偏移 | -123 | dBc/Hz | ||||

| 10MHz 頻率偏移 | -138 | dBc/Hz | ||||

| 相位雜訊433MHz | PN | 10 kHz 頻率偏移 | -105 | dBc/Hz | ||

| 100kHz 頻率偏移 | -108 | dBc/Hz | ||||

| 1MHz 頻率偏移 | -120 | dBc/Hz | ||||

| 10MHz 頻率偏移 | -140 | dBc/Hz | ||||

| 相位雜訊915MHz | PN | 10 kHz 頻率偏移 | -100 | dBc/Hz | ||

| 100kHz 頻率偏移 | -103 | dBc/Hz | ||||

| 1MHz 頻率偏移 | -113 | dBc/Hz | ||||

| 10MHz 頻率偏移 | -132 | dBc/Hz |

2.4.3 參考時鐘規格要求

外接參考時鐘典型規格如下:

| 參數 | 符號 | 條件 | 最小值 | 典型值 | 最大值 | 單位 |

| 晶體頻率1 | FXTAL | 26 | MHz | |||

| 晶體頻率容差2 | ppm | 20 | ppm | |||

| 負載電容 | CLOAD | 7.3 | pF | |||

| 晶體啟動時間3 | tXTAL | 400 | us |

備註:

- 晶體電路可以直接用外部參考時鐘通過耦合電容接到XIN 管腳上工作。 外部時鐘信號的峰峰值要求在0.3 到 1.0 V 之間。

- 該值包括 (1) 初始誤差; (2) 晶體負載; (3) 老化;和(4) 隨溫度的改變。可接受的晶體頻率誤差受限於接收機的帶寬和與之搭配的發射器之間射頻頻率偏差。

- 該參數很大程度上與晶體相關。

2.4.4 S-FSK®模式電氣規範

表 23 S-FSK模式电气规格

| 參數 | 符號 | 描述 | 最小 | 典型 | 最大 | 單位 | |

| 碼片速率 | CR | 碼片速率12kcps | 0.21 | 1.87 | Kbps | ||

| 碼片速率24kcps | 0.42 | 3.75 | Kbps | ||||

| 碼片速率48kcps | 0.84 | 7.5 | Kbps | ||||

| 碼片速率100kcps | 1.75 | 15.6 | Kbps | ||||

| 碼片速率200kcps* | 3.51 | 31.2 | Kbps | ||||

| 輸出功率 | Pout | TX輸出 | -20 | 22 | dBm | ||

| 輸出功率步進 | P_STEP | TX輸出 | 1 | 2 | dB | ||

| 不同溫度下輸出功率變化 | P_TEMP | 3 | dB | ||||

| 1db壓縮點 | P1db | TX輸出 | 16 | dBm | |||

| 發射鄰道洩漏 | ACLR | Adjacent Upper | CR =12kcpsBW=12.8kHz Channel Space = 25kHz | 32 | dBc | ||

| Adjacent Under | 34 | dBc | |||||

| Alternate Upper | 48 | dBc | |||||

| Alternate Under | 50 | dBc | |||||

| Adjacent Upper | CR =24kcpsBW=25kHz Channel Space = 50kHz | 37 | dBc | ||||

| Adjacent Under | 37 | dBc | |||||

| Alternate Upper | 55 | dBc | |||||

| Alternate Under | 55 | dBc | |||||

| Adjacent Upper | CR =48kcpsBW=50kHz Channel Space = 100kHz | 37 | dBc | ||||

| Adjacent Under | 38 | dBc | |||||

| Alternate Upper | 56 | dBc | |||||

| Alternate Under | 56 | dBc | |||||

| Adjacent Upper | CR =100kcpsBW=120kHzChannel Space = 200kHz | 36 | dBc | ||||

| Adjacent Under | 38 | dBc | |||||

| Alternate Upper | 58 | dBc | |||||

| Alternate Under | 58 | dBc | |||||

| 接收靈敏度470MHz | SEN | CR = 12kcps | SF=5 | -124 | dBm | ||

| SF=6 | -131 | dBm | |||||

| SF=7 | -134 | dBm | |||||

| SF=8 | -137 | dBm | |||||

| SF=9 | -140 | dBm | |||||

| SF12* | -148 | dBm | |||||

| CR = 24kcps | SF=5 | -121 | dBm | ||||

| SF=6 | -126 | dBm | |||||

| SF=7 | -130 | dBm | |||||

| SF=8 | -134 | dBm | |||||

| SF=9 | -137 | dBm | |||||

| CR = 48kcps | SF=5 | -118 | dBm | ||||

| SF=6 | -126 | dBm | |||||

| SF=7 | -128 | dBm | |||||

| SF=8 | -130 | dBm | |||||

| SF=9 | -133 | dBm | |||||

| CR = 100kcps | SF=5 | -115 | dBm | ||||

| SF=6 | -122 | dBm | |||||

| SF=7 | -124 | dBm | |||||

| SF=8 | -127 | dBm | |||||

| SF=9 | -131 | dBm | |||||

| 同通道干擾抑制比 | Co_REJ | CR = 12kcps; SF = 9; Pw= 接收靈敏度 + 3 dBCW干擾, PER<5% | 10 | dBc | |||

| CR = 12kbps; SF = 9; Pw= 接收靈敏度 + 3 dB同調制干擾, PER<5% | 10 | dBc | |||||

| 鄰道抑制比 @ 470MHz | 1CH_REJ | CR = 12kbps; Pw= 接收靈敏度 + 3 dBBW= 12kHz, Channel Space = 25kHzCW干擾, PER<5% SF = 5SF = 9 | 4860 | dBc | |||

| 2CH_REJ | CR = 12kbps; SF = 9; Pw= 接收靈敏度 + 3 dBBW= 12kHz, Channel Space = 50kHz, CW干擾, PER<5% SF = 5SF = 9 | 6072 | dBc | ||||

| 阻塞抑制 | Block | ±1 MHz | CR = 12kbps; SF = 9; BW= 12kHz; Pw= 接收靈敏度 + 3 dBCW干擾,PER<5% | 82 | dBc | ||

| ±2MHz | 86 | dBc | |||||

| ±10 MHz | 95 | dBc | |||||

| 接收動態範圍 | RDR | 最大接收動態範圍 | SEN | 0 | dBm | ||

| 接收通道帶寬 | BW | 接收通道帶寬 | 7 | 2000 | KHz | ||

| RSSI範圍 | RSSI | 步進1dB | -114 | -10 | dBm | ||

| 雜訊係數 | NF | f=470MHz | 4.5 | dB | |||

2.4.5 數字IO電氣特性

2.4.5.1 通用參數

| 符號 | 參數 | 條件 | 最小值 | 典型值 | 最大值 | 單位 |

| VIH | 輸入高電平電壓 | VCC =1.8V ~ 3.6V | Vcc*0.7 | – | V | |

| VIL | 輸入低電平電壓 | VCC =1.8V ~ 3.6V | – | Vcc*0.3 | V | |

| VOL | 輸出低電平 | VCC =1.8V ~ 3.6V | Vcc*0.8 | – | V | |

| VOH | 輸出高電平 | VCC =1.8V ~ 3.6V | – | Vcc*0.2 | V | |

| T_Rise | 上升沿時間 | 6 | ns | |||

| T_Fise | 下降沿時間 | 6 | ns | |||

| IO_CLK | IO時鐘頻率 | 40 | MHz |

2.4.5.2 GPIO

| 符號 | 參數 | 條件 | 典型值 | 單位 | ||

| GPIO_Drive | GPIO 0~4GPIO驅動能力 | VIO = 3.3 V,V_GPIO=2.65 | 6 | mA | ||

| RPU | 上拉電阻 | – | 200 | KΩ | ||

| RPD | 下拉電阻 | – | 200 | KΩ |

備註:所有GPIO均有上拉,下拉以及open drain三種配置,上下拉狀態睡眠均可保持;

3 電路描述

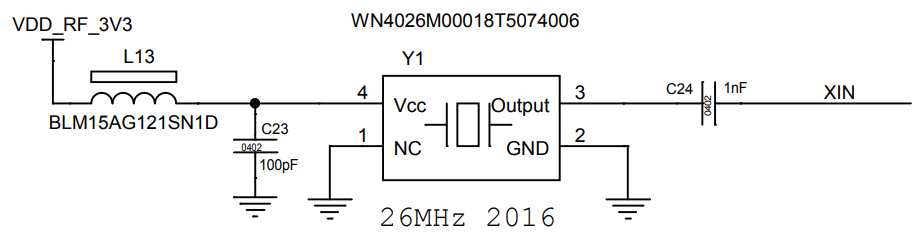

3.1 參考時鐘

TP6300的時鐘系統,包含內部高速RC時鐘和支持外接RTC 32K時鐘。射頻參考時鐘可以根據系統符號率需求選擇26MHz石英晶體並同時支持有源時鐘如TCXO/VC-TCXO的輸入。

3.1.1 內部RC時鐘

TP6300內部集成兩個RC時鐘;一個為系統睡眠時提供RTC的LRC時鐘,在系統睡眠時保證定時喚醒計時器以及外部中斷喚醒,頻率為32KHz;另一個為睡眠喚醒後進入待機模式的HRC工作時鐘,用於外部參考時鐘尚未建立時給晶片內部提供一個較快的時鐘,典型頻率配置26M。

內部高速RC時鐘頻率穩定性較差,在晶片進入參考時鐘工作狀態後,可以對內部LRC進行校準,以保證睡眠時定時喚醒的準確性。推薦在每次睡眠之前都進行一次校準操作。

掉電後重新上電或者系統從睡眠喚醒起來,等待參考時鐘穩定後,系統應該儘量切換到精確的參考時鐘上工作。

3.1.2 晶體振盪電路

TP6300包含一個具有快速啟動的集成晶體振盪器。該電路支持24M~38.4M甚至更寬範圍的晶體頻率,用戶可以按照系統定義選擇適當的規格進行使用。

可以很容易地使用 TCXO 和外部信號源代替傳統的 XTAL,連接到 XIN 引腳上。建議使用收到的時鐘信號作為 500 mV 到 1V 間峰值擺動,並且交流耦合到 XIN 引腳上。當使用TCXO作為參考時鐘源時,XOUT 腳懸空處理。

為保證性能,推薦應用TCXO作參考時鐘,連接方式如下圖所示:

- 圖 3.1 TCXO 參考時鐘連接電路

如果 TCXO 輸出幅度過大,可以減小隔直電容 C24進行調節。

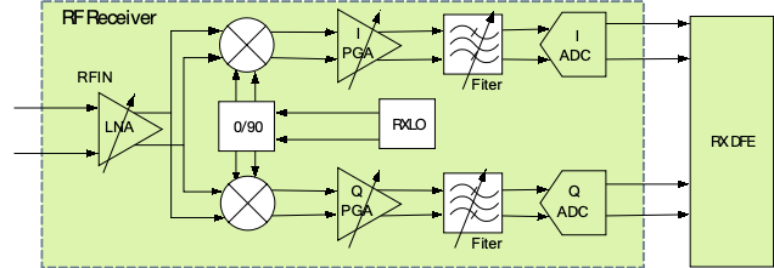

3.2 接收機

TP6300射頻接收機框圖如下圖所示,接收到的空口射頻信號經過天線接收首先通過差分低雜訊放大器(LNA)進行放大,再採用正交混頻器混頻處理並經過中頻放大器放大,接著到模擬濾波器進行雜波濾除。模擬濾波器可以根據需要設置為低通濾波器或者帶通濾波器。為了避免直接變頻架構帶來的鏈路殘餘直流影響,工作在低速率窄帶寬時推薦使用低中頻接收架構,濾波器設置為帶通濾波器。當系統工作在在高速率大帶寬時,可以使用零中頻架構,濾波器此時設置為低通模式。其中模擬濾波器可以從6.5KHz~2MHz帶寬可調節,具體的設置請參考編程指南或者相應的參考設置程式。

- 圖 3-2 接收機框圖

經過濾波後的I和Q信號由連續時間回饋架構的ΣΔ模數轉換器(ADC)進行數位化。進入數字域後,信號經過數字前端(DFE)模組進行抽取、數字下變頻、數字通道濾波等處理後產生數字基帶信號,最後根據調製方案(FSK數據機或S-FSK®數據機)由選定的數據機進行解調。

1.1.1 接收中頻

TP6300接收器S-FSK®模式主要工作在低中頻配置下。

表 31 接收中頻配置映射表

| 配置名稱 | 濾波器帶寬(kHz SSB) | 接收中頻(kHz) |

| S-FSK_CR_12 | 8.5 | 49 |

| S-FSK _CR_24 | 13.5 | 49 |

| S-FSK _CR_48 | 32.5 | 49 |

| S-FSK _CR_100 | 85 | 101 |

| S-FSK _CR_200 | 110 | 138 |

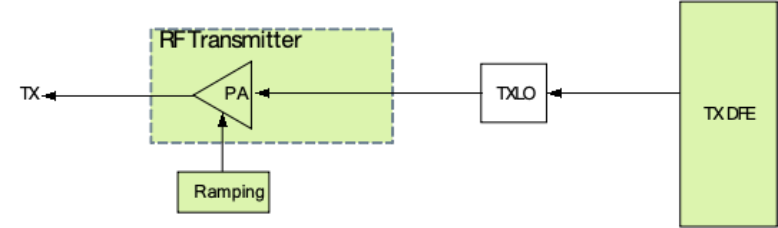

3.3 發射機

TP6300的發射機框圖如下圖所示,基帶數字信號經過數字前端處理後送給發射機進行發射。這裏採用非線性調製信號,直接在TXPLL上直接進行調製然後給高效率E類功率放大器進行放大再由天線發射。

- 圖 3-3 發射機框圖

4 TP6300數字調製解調設計

4.1 S-FSK®數據機

S-FSK®數據機採用擴頻調製技術,與傳統的基於FSK的調製相比,顯著提高了無線電通信鏈路的覆蓋範圍和魯棒性。S-FSK®數據機的一個重要特性是其對干擾的高免疫能力。S-FSK®數據機能夠實現高達15dB的同頻FSK干擾抑制。這種抗干擾能力使得S-FSK®調製系統能夠在頻譜使用密集的頻段或混合通信網絡中簡單共存,尤其是在傳統調製方案失效時,S-FSK®可用於擴展覆蓋範圍。

4.1.1 調製參數

針對特定應用優化S-FSK®調製,設計者可以調整幾個關鍵設計參數,每個參數都允許在鏈路預算、抗干擾能力、頻譜佔用和數據速率之間進行權衡。這些參數包括:

碼片速率(CR)

擴頻因數(SF)

調製編碼方案(MCS)

4.1.1.1 碼片速率

碼片速率的提高對應信號帶寬也會增加,同時可以使用更高的有效數據速率,從而減少了傳輸時間,但以降低接收靈敏度為代價。可支持的S-FSK®碼片速率如下表所示:

表 41 S-FSK碼片速率映射表

| 碼片速率索引 | 0 | 1 | 2 | 3 | 4 |

| 碼片速率CR(kcps) | 12 | 24 | 48 | 100 | 200 |

接收機先在射頻鏈路中將信號變頻至低中頻,然後在數字域下變頻至基帶。

4.1.1.2 擴頻因數

S-FSK®擴頻調製是通過用擴頻碼本調製後的多個碼片資訊來表示有效載荷資訊。對於擴頻因數SF,每個SIMS符號有2SF 個碼本,對應2SF 個碼片,每個符號所能承載的比特數為SF。

需要注意的是:無線鏈路的收發雙方都必須提前知道擴頻因數,因為不同的擴頻因數彼此正交。

S-FSK®接收器能夠接收負信噪比的信號,這提高了其靈敏度以及鏈路預算和覆蓋範圍。用戶可以根據應用和覆蓋需要選擇合適的擴頻因數。

表 42 不同擴頻因數S-FSK解調門限

| 擴頻因數(SF) | 5 | 6 | 7 | 8 | 9 |

| 碼片數/SIMS符號 | 32 | 64 | 128 | 256 | 512 |

| S-FSK解調門限(dB) | -2.5 | -5 | -7.5 | -10 | -12.5 |

4.1.1.3 調製編碼方案

MCS是S-FSK無線通信系統中用於配置物理層傳輸速率的索引機制,它通過將調製方式、編碼率等影響速率的參數組合編制為索引表,每個MCS索引對應一組特定參數下的物理傳輸速率。在S-FSK無線通信系統中,MCS採用3位字段表示,包含多種不同的調製和編碼方案組合。

4.1.2 S-FSK物理層幀結構

S-FSK®數據機採用顯式數據包格式,顯式數據包包含一個簡短的頭部,其中包含有關數據包的位元組數、調製編碼方案等資訊。數據包格式如下圖所示。

| SHR | PHR | Payload | Payload CRC | |

| Header | CRC | |||

物理層幀頭PHR默認採用MCS1。

4.1.3 S-FSK通道活躍檢測(CAD)

採用擴頻調製技術時,接收機的接收靈敏度可以遠低於接收機雜訊,如何確定通道是否存在有用信號存在挑戰。在這種情況下,使用接收信號強度指示(RSSI)顯然是不切實際的。在TP6300中,通道活動檢測器被設計為能夠檢測S-FSK®前導碼的存在。一旦進入CAD模式,TP6300將對配置的頻點進行掃描,如果在CAD期間檢測到S-FSK®符號,將返回通道活動檢測中斷請求。

5 數字介面

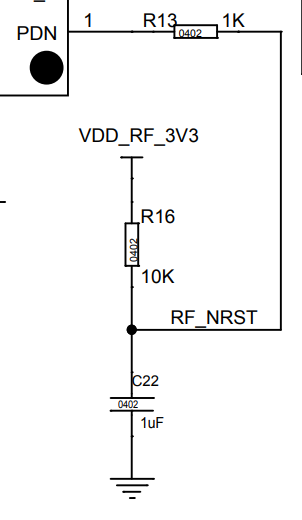

5.1 複位

可以通過切換引腳PDN來對晶片進行完整的“恢復出廠設置”,隨後將自動執行標準校準程式,且之前的所有上下文資訊都將丟失。通常情況下,需要將該引腳保持低電平不低於40毫秒才能完成複位。

- 圖 5-1 RST 信號連接電路

5.2 SPI介面

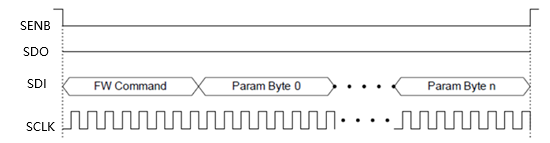

TP6300通過標準 4 線週邊介面 (SPI) 與主機進行通訊。SCLK、SDI、SDO 和 SENB。圖5-2展示了 SPI 寫命令格式。SENB 引腳應降低以啟動 SPI 命令。SDI 數據的第一個位元組會成為後面緊接 n 個參數數據的位元組固件命令其中之一,這些參數數據字節會根據具體命令進行變化。SCLK 的上升沿應與 SDI 數據的中心對齊。

- 圖 5-2 SPI 寫命令

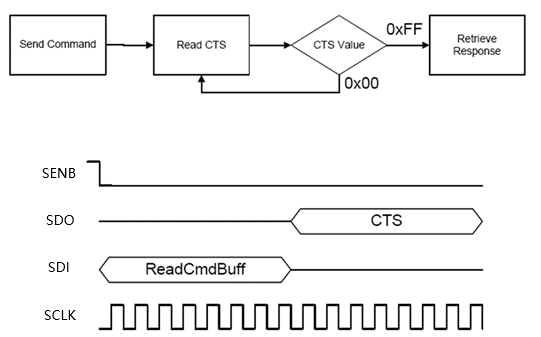

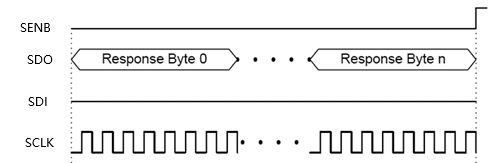

TP6300 包含內部控制器,可控制無線電的所有內部功能。對於 SPI 讀取命令,一般的控制器檢測清除發送流程用來確保內部控制器已執行命令,並已將數據準備好通過 SDO 引腳輸出。圖2展示了 SPI 讀取命令的一般流程。一旦CTS 值顯示 FFh 那麼讀出的數據就即將會時鐘輸出到主機 MCU。圖3展示了在 CTS 被設置為 FFh 後的讀取週期。內部 MCU 會在下降沿時鐘輸出 SDO 數據以便主機 MCU 能夠在SCLK 的上升沿處理 SDO 數據。

- 圖 5-3 SPI 讀命令-檢查CTS

- 圖 5-4 SPI 讀命令-隨時鐘扇出數據

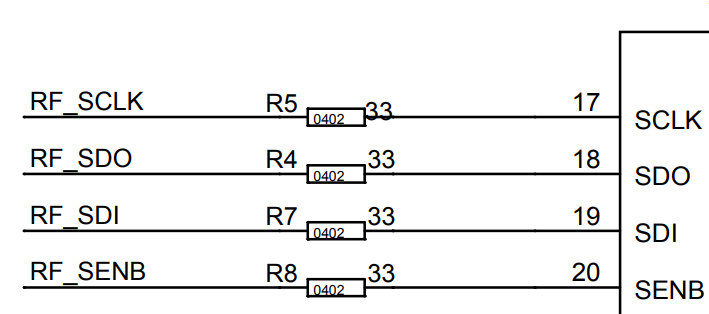

主機通過SPI介面對TP6300進行配置以及程式下載,時鐘速度應小於 40MHz。

TP6300 SPI介面與主機之間的連接要串接22Ω或33Ω電阻,否則在高速傳輸數據時會影響信號品質和完整性。

- 圖 5-5 SPI 介面連接電路

5.3 複用數字介面

5.3.1 數字IO引腳映射

| 工作模式 | GPIO0 | GPIO1 | GPIO2 | GPIO3 | GPIO4 |

| 接收 | 預留 | 預留 | 接收時低電平 | FIFO burst完成中斷 | 低電平 |

| 發射 | 預留 | 預留 | 發射同步信號,高有效 | FIFO burst寫完成中斷 | 發射完成中斷 |

| 其他 | 預留 | 預留 | 低電平 | 低電平 | 低電平 |

5.4 中斷

5.4.1 發射中斷

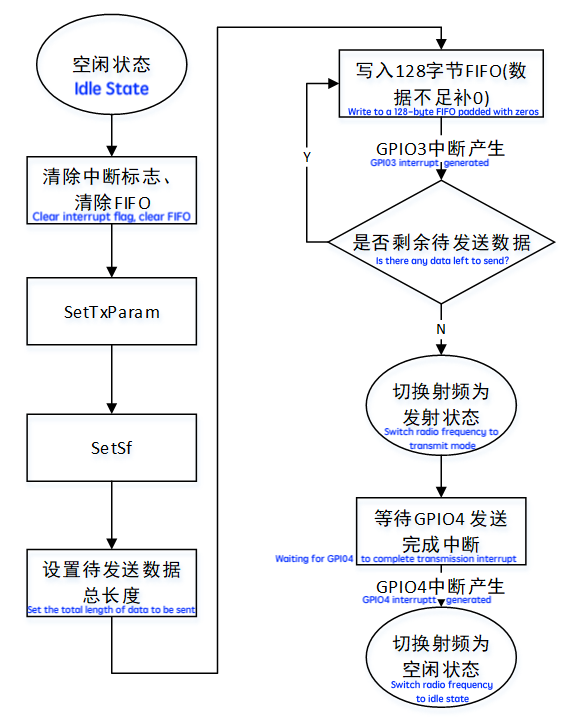

TP6300採用用戶數據統一編碼發送方式, 在切換射頻發射模式前, 需要完成所用用戶數據的輸入;

用戶預先設置發送數據長度位元組;

按照128位元組寫入FIFO,寫入完成後,等待GPIO3發送數據中斷信號;

發射數據中斷信號產生後,如有剩餘數據繼續寫入FIFO,否則切換射頻為發射模式並等待GPIO4發射完成中斷;

射頻按照配置參數發射完成後,產生GPIO4 發射完成中斷。

5.4.2 接收中斷

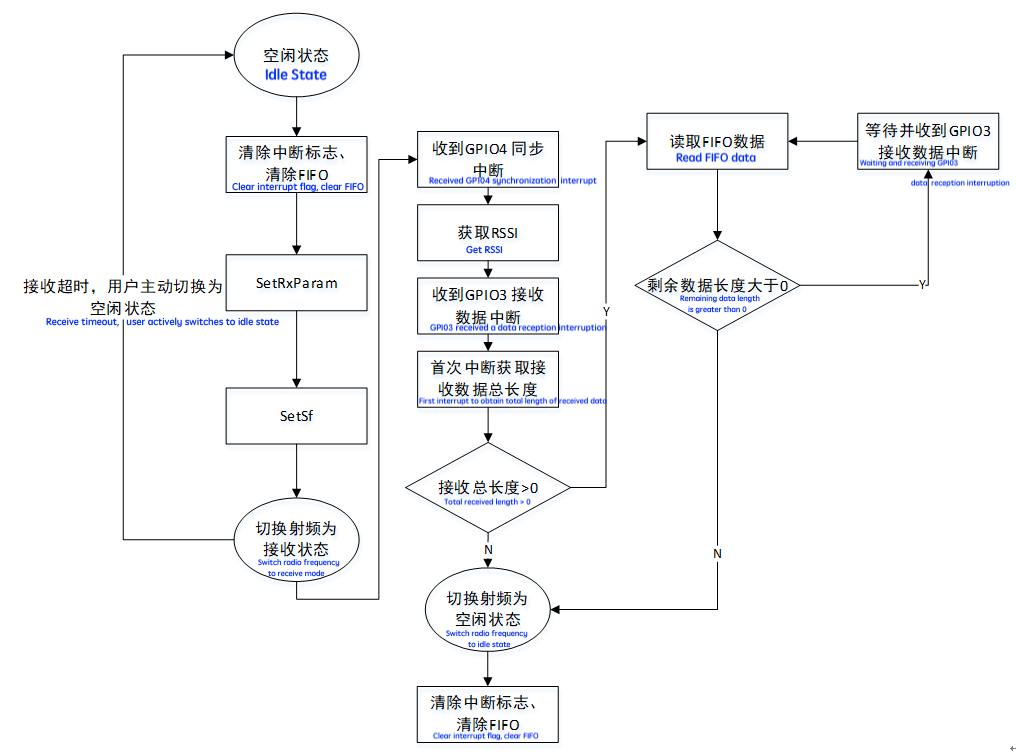

射頻進入接收模式後,如果收到同步信號,則產生GPIO4 接收同步中斷,用戶此時可獲取接收信號強度,並維持接收模式等待 GPIO3 接收數據中斷;

收到GPIO3 接收數據中斷後,清除中斷,獲取接收數據長度,並通過FIFO讀取128位元組數據;

如有剩餘數據接收則等待GPIO3 接收數據中斷,否則切換射頻為空閒模式。

6 模擬介面

6.1 電源

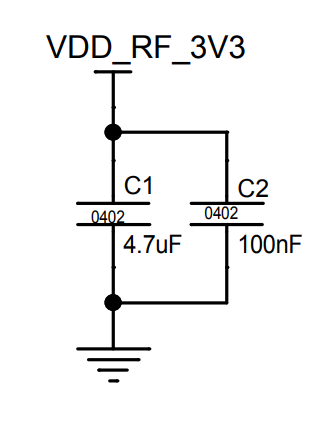

電源範圍為1.8V~3.6V,推薦3.3V,建議對地加4.7uF和100nF兩個去耦電容。

- 圖 6-1 輸入電源

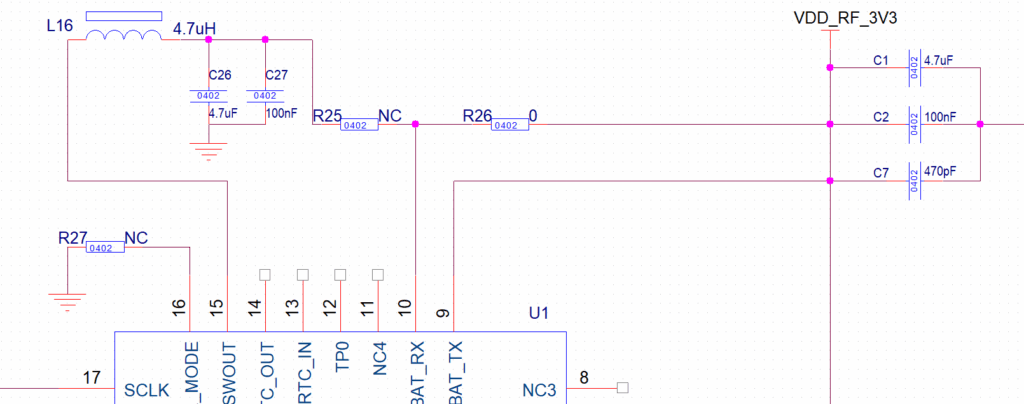

晶片內部有LDO和DCDC兩種工作模式,由管腳PWR_MODE硬體連接決定。

PWR_MODE:

- 懸空 =LDO模式,VBAT _RX與VBAT _TX共用外部供電

- 接低=DCDC模式,VBAT_RX接Pin15 SWOUT供電

如下為PMU部分的參考設計電路,電感L16 4.7uH選型時電流至少0.5A:

| PMU模式 | R27 | R25 | R26 |

| LDO模式 | NC | NC | 0Ω |

| DCDC模式 | 0Ω | 0Ω | NC |

- 圖 6-2 PMU部分參考設計

6.2 溫度檢測

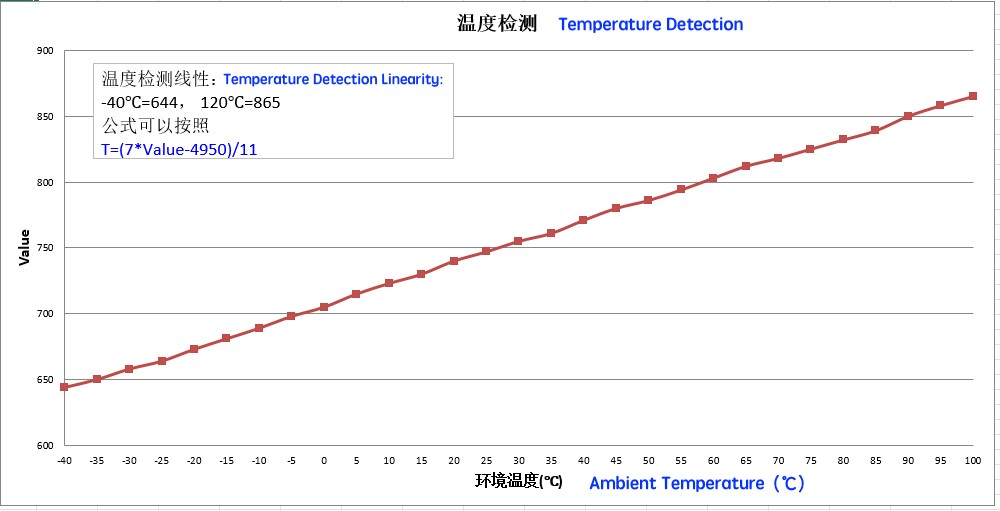

TP6300晶片內置了溫度計功能,可以實現對晶片溫度的讀取和某些溫度特性的補償比如晶體溫度的偏移,發射功率的溫度補償等。檢測曲線如下圖所示

- 圖 6-3 內部溫度計讀數特性

6.3 電壓檢測

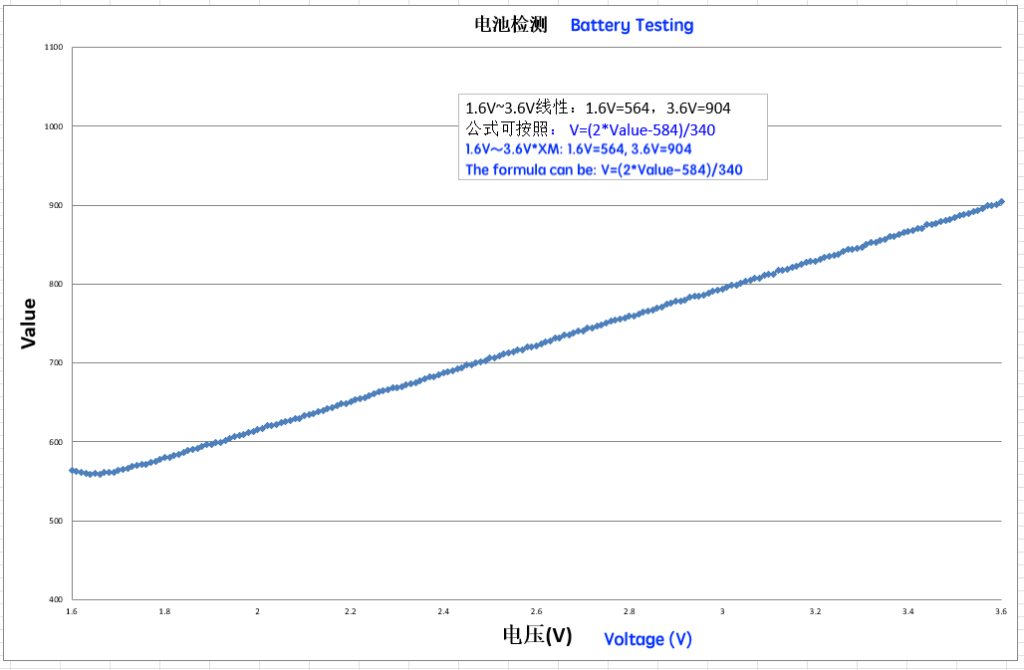

TP6300晶片通過對晶片VBAT的檢測,實現電源對晶片供電的監控,從而實現低電壓關機或者產生中斷或者複位。電池電壓可工作在1.8V~3.6V電池電壓檢測曲線如下圖所示:

- 圖 6-4 電池電壓檢測特性

7 命令字介面

命令字格式:

| 位元組序 | 描述 |

| 0 | CMD :命令字 |

| 1 | TYPE :消息類型 |

| 2 | MSG_ID:消息ID |

| 3 | LEN :數據總長度(1~16) |

| 4 | OFFSET:數據偏移量 |

| 5~N | DATA:數據,N最大值是16(即單次最大下發12位元組) |

TYPE/MSG_ID 僅僅在 CMD_SET_PROPERTY 和CMD_GET_PROPERTY 命令字下有效,其他設置為0;

CMD/TYPE/MSG_ID 對應唯一的消息,消息數據最大長度為16位元組;消息數據大於12位元組時,需要拆分2條配置資訊下發。

CMD命令字 說明:

| CMD Value | 描述 |

| 0x11 | CMD_SET_PROPERTY 設置參數 |

| 0x12 | CMD_GET_PROPERTY 獲取參數 |

| 0x44 | CMD_READ_CMD_BUFF 查詢SPI CTS狀態 |

| 0x50 | CMD_FFRA_READ 獲取to host FIFO狀態 |

| 0x66 | CMD_WRITE_TX_FIFO 寫FIFO from host |

| 0x77 | CMD_READ_RX_FIFO 讀FIFO to host |

| TYPE | MSG_ID |

| 0x06 IPC_MSG_TPCTL | 0x03 ID_SET_FIFO 收發FIFO 使能 |

| 0x04 ID_CLEAR_FIFO 收發FIFO清空 | |

| 0x05 ID_RF_MODE 切換射頻狀態 | |

| 0x06 ID_TX_DATA_LEN 發送數據字節長度 | |

| 0x07 ID_SET_SF 設置擴頻因數 | |

| 0x08 ID_MOD_TYPE 設置調製方式 | |

| 0x0A ID_CLEAR_FLAG 清除拉低GPIO中斷 | |

| 0x0D ID_SET_TX_PARAM 設置發射射頻參數 | |

| 0x0E ID_SET_RX_PARAM 設置接收射頻參數 | |

| 0x0F ID_SET_DC_CAL 設置直流校準 | |

| 0x10 ID_RX_DATA_LEN 獲取接收數據總長度 | |

| 0x11 ID_RX_RSSI 獲取信號強度(dBm) | |

| 0x21 ID_CHECK_BUSY 檢查晶片空閒狀態 |

7.1 操作模式功能

| Byte | 0 | 1 | 2 | 3 | 4 | 5 |

| Data from host | 0x11 | 0x06 | 0x05 | 0 | 0 | new_mode |

new_mode: 0 – Stanby

1 – Rx

2 – Tx

7.2 FIFO讀寫

7.2.1 FIFO使能

| Byte | 0 | 1 | 2 | 3 | 4 |

| Data from host | 0x11 | 0x06 | 0x03 | 0 | 0 |

7.2.2 FIFO清空

| Byte | 0 | 1 | 2 | 3 | 4 |

| Data from host | 0x11 | 0x06 | 0x04 | 0 | 0 |

7.2.3 寫FIFO

設置待發送數據總長度,tx_len,超過128位元組時需要多次寫入TX FIFO;

| Byte | 0 | 1 | 2 | 3 | 4 | 5 | 6 |

| Data from host | 0x11 | 0x06 | 0x06 | 2 | 0 | tx_len[15..8] | tx_len[7..0] |

然後寫入TX FIFO 128位元組,數據不足時補0寫滿128位元組

| Byte | 0 | 1 | .. | .. | 128 |

| Data from host | 0x66 | Byte0 | .. | .. | Byte127 |

7.2.4 讀FIFO

首先獲取待接收數據總長度,rx_len,超過128位元組時需要多次讀取RX FIFO;

| Byte | 0 | 1 | 2 | 3 | 4 |

| Data from host | 0x11 | 0x06 | 0x10 | 2 | 0 |

| Byte | 0 | 1 | 2 | 3 | 4 |

| Data from host | 0x12 | 0x06 | 0x10 | 2 | 0 |

| Byte | 0 | 1 | |||

| Data to host | rx_len[15..8] | rx_len[7..0] | |||

然後獲取當次RX FIFO數據長度(rx_fifo_len : 0 到128 位元組)

| Byte | 0 | |||

| Data from host | 0x50 | |||

| Byte | 0 | 1 | 2 | 3 |

| Data to host | rx_fifo_len | tx_fifo_len | RES1 | RES2 |

再讀當次RX FIFO數據

| Byte | 0 | 1 | .. | .. | rx_fifo_len |

| Data to host | 0x77 | DATA | .. | .. | DATA |

7.2.5 清除中斷標誌

| Byte | 0 | 1 | 2 | 3 | 4 |

| Data from host | 0x11 | 0x06 | 0x0A | 0 | 0 |

7.2.6 獲取信號RSSI資訊

| Byte | 0 | 1 | 2 | 3 | 4 |

| Data from host | 0x11 | 0x06 | 0x11 | 2 | 0 |

| Byte | 0 | 1 | 2 | 3 | 4 |

| Data from host | 0x12 | 0x06 | 0x11 | 2 | 0 |

| Byte | 0 | 1 | |||

| Data to host | rssi[15..8] | rssi[7..0] | |||

7.3 S-FSK調製解調功能

7.3.1 SetTxParams

| Byte | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 |

| Data from host | 0x11 | 0x06 | 0x0D | 7 | 0 | freqKHz | chipRate | txPwr | ||||

| [31..24] | [23..16] | [15..8] | [7..0] | [15..8] | [7..0] | |||||||

freqKHz: :發送信號頻點,單位KHz

chipRate: 發送信號碼片速率,當前支持 12/24/48/100/200 kcps

txPwr:: 發送信號功率,dBm,範圍[-20, 22]dBm

7.3.2 SetRxParams

| Byte | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 |

| Data from host | 0x11 | 0x06 | 0x0E | 7 | 0 | freqKHz | chipRate | rxAgc | ||||

| [31..24] | [23..16] | [15..8] | [7..0] | [15..8] | [7..0] | |||||||

freqKHz: :接收信號頻點,單位KHz

chipRate: 接收信號碼片速率,當前支持 12/24/48/100/200 kcps

rxAgc: 接收增益控制,0: 接收機自動增益控制;其他[4,15] 固定的接收增益檔位值

7.3.3 SetSf

| Byte | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 |

| Data from host | 0x11 | 0x06 | 0x07 | 4 | 0 | preamSfInit | dataSfInit | sf | mcs |

發送機發送參數和接收機接收對應參數要求一致。

preamSfInit/dataSfInit: 建議配置不同的值以區分pream 和數據;收發雙方需保證參數一致。

sf::擴頻因數,配置範圍 [5, 9],擴頻因數越大,相同數據空口發送時間越長;收發雙方需保證參數一致。

mcs:調製編碼方案,當前配置範圍[0,1],0表示SIMS調製碼本全部使用,1表示SIMS調製碼本使用一半。

7.4 狀態資訊

7.4.1 DC直流校準

射頻空閒StandBy 狀態時進行直流校準,射頻直流校準約需要150ms完成,期間不要配置TP6300;

| Byte | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 |

| Data from host | 0x11 | 0x06 | 0x0F | 6 | 0 | freqKHz | chipRate | ||||

| [31..24] | [23..16] | [15..8] | [7..0] | [15..8] | [7..0] | ||||||

freqKHz: 直流校準的頻點,單位KHz,推薦設置工作頻點範圍附近;如工作在470000kHz ~ 510000kHz,建議設置為 465000

chipRate: 直流校準時對應的碼片速率,單位kcps,與接收機工作的碼片速率一致,當前支持 12/24/48/100/200 kcps。

7.4.2 檢查射頻配置狀態

射頻參數配置完成後,需要檢查射頻配置狀態,返回0xFF表示射頻配置空閒,可以進行下一條指令的配置。

| Byte | 0 | 1 | 2 | 3 | 4 |

| Data from host | 0x12 | 0x06 | 0x21 | 1 | 0 |

| Byte | 0 | ||||

| Data to host | chipStatus | ||||

chipStatus: 0xFF: 射頻空閒,可以配置下一條指令;

其他,射頻忙,等待射頻空閒。

8 應用

8.1 主機API基本讀寫功能

與TP6300的通信圍繞通用功能展開,這些功能允許用戶對設備的行為進行控制。每個功能都基於一個操作命令(在本文檔中稱為“操作碼”),隨後是一組參數。在以下章節中,假設主機微控制器具有SPI,並通過spi.write(data)訪問它。SPI晶片選擇由SENB定義,低電平有效。

8.2 基本發射操作電路配置

- 圖 8-1 基本發射配置流程圖

8.3 基本接收操作電路配置

- 圖 8-2 基本接收配置流程圖

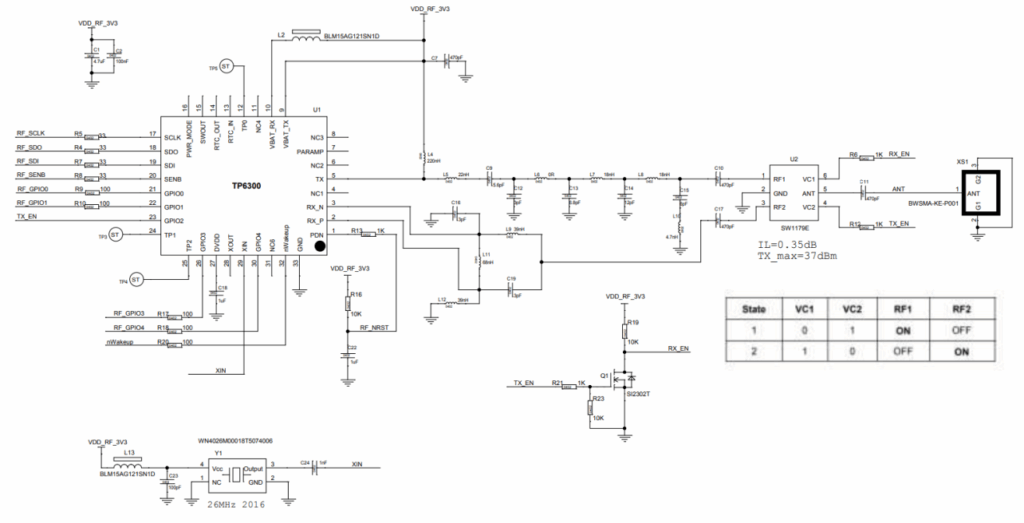

8.4 應用電路

- 圖 8-3 帶射頻開關的參考電路

具體電路應用詳見《TP6300硬體設計指南》。

9 縮略語表

| 縮略語 | 全稱 | 中文含義 |

| ACR | Adjacent Channel Rejection | 相鄰通道抑制 |

| 12ACLR | Adjacent Channel Leakage Ratio | 鄰道洩漏比 |

| ADC | Analog-to-Digital Converter | 模數轉換器 |

| BW | Bandwidth | 帶寬 |

| CAD | Channel Activity Detection | 通道活躍檢測 |

| CW | Continuous Wave | 連續波形 |

| CR | Chip Rate | 碼片速率 |

| CRC | Cyclical Redundancy Check | 迴圈冗餘校驗 |

| DC-DC | Direct Current to Direct Current Converter | 直流-直流轉換器 |

| DFE | Digital Front End | 數字前端 |

| FIFO | First In First Out | 先入先出 |

| FSK | Frequency Shift Keying | 頻移鍵控 |

| GPIO | General Purpose Input/Output | 通用輸入/輸出口 |

| HRC | High frequency Resistance & Capacitance Oscillator | 高頻RC振盪器 |

| LDO | Low-Dropout | 低壓差 |

| LNA | Low Noise Amplifier | 低雜訊放大器 |

| LRC | Low frequency Resistance & Capacitance Oscillator | 低頻RC振盪器 |

| MCS | Modulation Coding Scheme | 調製與編碼方案 |

| NF | Noise Factor | 雜訊係數 |

| PER | Packet Error Ratio | 誤包率 |

| RC | Resistance & Capacitance | RC振盪器 |

| RDR | Receiver Dynamic Range | 接收動態範圍 |

| RSSI | Received Signal Strength Indicator | 接收信號強度指示 |

| S-FSK® | SIMS – FSKthe S-FSK® Mark is a registered trademark of the Techphant Corporation | 序列索引調製擴頻頻移鍵控,S-FSK®是技象公司註冊商標 |

| SF | Spread Factor | 擴頻因數 |

| SIMS | Sequence Index Modulation Spread | 序列索引調製擴頻 |

| SPI | Serial Peripheral Interface | 串行外設介面 |

| SNR | Signal to Noise Ratio | 信噪比 |

| SSB | Single Side Band | 單邊帶 |

| TCXO | Temperature-Compensated Crystal Oscillator | 溫度補償晶體振盪器 |

10 修訂歷史

| 版本 | 發佈日期 | 修訂內容 |

| 1.0 | 2025.12.2 | 首次發佈 |